热门关键词:

手机快充、通信设备、工业自动化、汽车电子……这些场景看起来离得很远,但它们有一个共同的“隐形门槛”:电源管理必须又稳、又省、还要扛得住负载突然抽风式的变化。

也正因为如此,降压型电源管理芯片(PMIC)里那颗Buck,从来不是“把电压降下来”这么简单——真正拉开差距的,是效率、瞬态响应、稳定性,以及在轻载到重载之间来回切换时,能不能一直保持体面。

这篇文章就围绕一个明确目标展开:一款基于180nm CMOS工艺实现的高性能双通道降压型电源管理芯片,Buck在400mA负载下峰值效率达到94.2%,并且在1mA–1.5A的宽负载范围内效率大于77%。它到底靠什么做到的?

很多电源指标最容易“看着强”,也最容易“用着难”。

因为真实系统里,负载不是线性的:待机时可能只有1mA级别,某个模块醒来瞬间就拉到数百mA甚至更高;再叠加射频、基带、传感器等子系统的动态行为,电源这边看到的就是连续的突发变化。

所以这类芯片设计的关键,从一开始就不是只盯着“峰值效率”,而是要回答更难的问题:

轻载怎么省?

重载怎么扛?

轻重载切换时怎么不乱?

效率和瞬态响应能不能同时要?

参考材料里给出的路线非常明确:Buck在重载与轻载分别工作于PWM与省电模式PSM,并配合一个时钟管理方案,把效率撑到了一个“宽范围都能看”的水平——1mA到1500mA都能保持较高效率表现。

从系统层面理解会更直观:

PWM(脉宽调制)更适合重载:开关频率与控制策略更利于稳定输出与提供更强的供电能力,也更容易在大电流下维持效率与响应。

PSM(省电模式)更适合轻载:轻载时如果还用重载那套“高频、持续开关”的方式,很多损耗并不是来自输出功率,而是来自控制与开关本身的固定开销。省电模式的意义,就是尽量减少这些不必要的消耗。

材料中提到这款Buck通过PWM/PSM双模式覆盖从1mA到1.5A的负载跨度,并且借助所提出的时钟管理方案在宽负载范围内实现高效率,这背后的设计取向很清晰:不把一种模式硬撑到全场景,而是让不同模式在各自擅长的区域发挥优势。

如果说双模式解决的是“不同负载区间用不同策略”,那么材料中提到的两点——关断时间技术与峰值电流模式复用——更像是在回答“策略切换与动态变化时,怎么仍然稳、仍然快”。

参考材料明确给出:针对高效率、高瞬态响应的应用需求,完成Buck设计,并提出:

关断时间技术(off-time technique)

峰值电流模式复用(peak current mode multiplexing)

结合双路输出误差放大器以获得良好的瞬态响应与稳定性

这些关键词摆在一起,其实在讲同一个工程现实:

电源的瞬态响应不是“运气好就快”,而是控制环路、误差放大、限流检测等一整套机制协同后的结果。尤其当负载电流快速变化时,控制策略要能迅速做出正确动作,否则输出电压就会出现明显过冲/欠冲。

材料里的测试结果也把“快”量化得很具体:

在1.76A/µs的负载电流摆率变化下,Buck输出的尖峰电压不超过207mV,响应时间小于42µs。这类指标的价值在于:它不是实验室里“慢慢调负载”得到的漂亮曲线,而是对“突发变化”这种现实问题的正面应对。

很多人谈PMIC,容易只盯功率级,忽略基准与噪声的底层影响。但电源管理芯片的“稳定感”,往往来自一些不显眼的模块——比如基准。

材料中提出:为进一步提升系统性能,提出一种超高电源抑制比、低噪声、低功耗的带隙基准电路,并将其应用于Buck电路中。

带隙基准看起来“不输出大电流”,但它决定了系统里许多关键参考与偏置的“基准线”是否干净、是否抗干扰。

当输入电源有波动、系统里开关噪声更复杂时,高电源抑制比(PSRR)的基准能显著降低这些扰动在控制与参考层面的传播风险,从而帮助Buck在动态场景里保持一致的表现。

这款芯片并不只有Buck。参考材料说明它还完成了快速响应无片外电容低压差线性稳压器(CL-LDO)设计,面向的是高电源抑制比、高负载调整性能需求,并提出:

改进型翻转电压跟随器

内部多反馈环路设计

环路补偿方案

实现快速瞬态响应、超低且不受负载电流影响的线性调整率、以及低频段良好的电源抑制

测试与后仿真数据同样给得很硬:

CL-LDO在0.14A/µs负载电流摆率变化下,尖峰电压不超过220mV,响应时间小于1.95µs

后仿真中线性调整率与负载调整率分别为8.25µV/V与4.18µV/A

1Hz与1kHz的PSRR分别为-106dB与-74.2dB

把Buck与CL-LDO放在同一颗降压型PMIC里,本质上是对“系统电源树”的现实妥协:

有的电路需要效率,有的电路更怕噪声、有的更需要低频抑制与稳定的线性供电。把两类稳压方式组合起来,才更贴近移动设备、通信设备等复杂系统的真实需求。

如果只看概念,所有电源方案都能说得头头是道;但工程世界最终看的是参数是否能落在一张表上。

参考材料给出的芯片实现信息是:

工艺:180nm CMOS

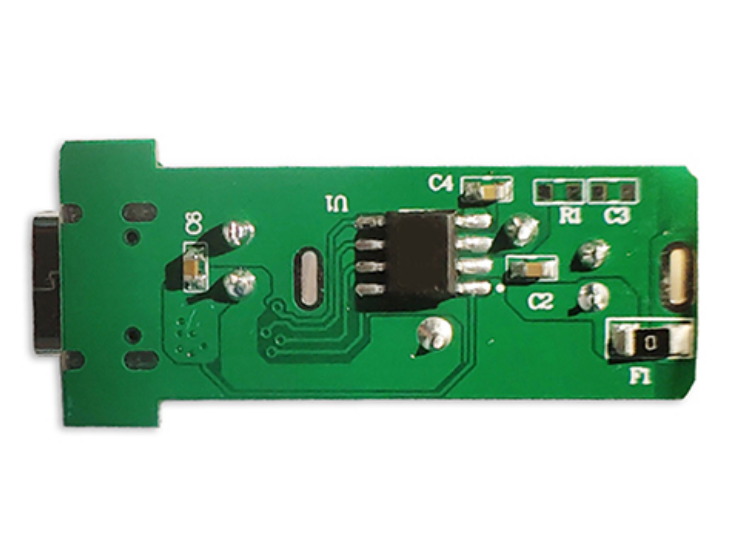

面积:1100µm × 655µm

Buck输入范围:2.5V–3.6V

CL-LDO输入范围:3.0V–3.6V

静态电流:Buck 18.4µA,CL-LDO 182µA

Buck效率:400mA时峰值94.2%;1mA–1.5A效率>77%

这些数字拼在一起,你会发现它讲的不只是“某个电路点子”,而是一套面向应用的综合权衡:效率、瞬态、PSRR、功耗、工艺与面积,缺一块都很难在真实产品里站稳。

一颗降压型PMIC的价值,往往不在于某个指标有多极限,而在于它能不能在各种负载、各种扰动、各种模式切换里保持稳定与一致。

这篇材料给出的路径很务实:

用PWM/PSM双模去覆盖宽负载区间,用关断时间技术与峰值电流模式复用去兼顾效率与瞬态,用双路输出误差放大器去稳住环路表现,再用超高PSRR带隙把系统底盘打牢,同时用CL-LDO去补对噪声与抑制更敏感的供电场景。