热门关键词:

同步整流IC作为电力电子领域提升效率的关键技术,其精度问题直接影响电路性能与可靠性。以下从技术原理、精度挑战、应用场景及优化策略四个维度展开分析。

一、同步整流IC的核心功能与精度关联

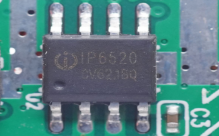

同步整流技术通过低导通电阻的功率MOSFET替代传统整流二极管,利用专用IC控制MOSFET的导通与关断,从而降低整流损耗。这一过程中,IC需实时监测MOSFET两端的电压(Vds)并作出判断。例如,当SR FET导通时,体二极管产生的负电压会触发驱动信号,此过程类似“用精密仪器测量电压波动”,任何信号偏差都可能导致误判。

二、精度的关键影响因素

寄生参数干扰:DRAIN引脚(连接MOS管漏极)与SR_GND引脚(连接源极)的布线若存在寄生阻抗,会导致Vds监测失真。这如同“用扭曲的望远镜观察星辰”,信号畸变可能引发提前关断或延迟导通,严重影响效率。

阈值比较机制:同步整流IC通过对比MOSFET两端电压与预设阈值决定驱动信号。例如,FM9919E等芯片需在DCM和QR模式下动态调整阈值,确保MOSFET在最佳时机切换。

内部电路设计:不同IC的效率差异不仅源于外部布线,更与其内部采样精度相关。例如,副边同步整流芯片需集成高精度ADC模块,以毫伏级分辨率捕捉电压变化。

三、精度不足的实际应用后果

效率损失:若Vds监测延迟,MOSFET可能长时间处于非理想状态,导致功耗增加。测试数据显示,精度失准可能使转换效率下降2%-5%。

热稳定性风险:误判的开关动作会产生异常发热,尤其在高频率场景(如5V充电器)中,可能引发器件失效。

兼容性问题:在多拓扑(如DCM与QR模式)切换时,精度不足可能导致策略混乱,影响适配器或充电器的输出稳定性。

四、提升精度的工程实践

布局优化:缩短DRAIN与SR_GND的走线长度,采用多层板设计降低寄生电感,如同“为信号传输铺设高速公路”。

滤波与屏蔽:在Vds采样路径添加RC滤波电路,抑制高频噪声干扰,类似于“为监测信号安装防抖支架”。

IC选型适配:根据应用场景选择支持动态阈值调整的芯片,如FM9919E针对隔离型拓扑优化了Vds检测算法。

仿真验证:通过LTspice等工具模拟寄生参数影响,预先评估布线方案对精度的敏感度。

五、未来技术演进方向

随着GaN等宽禁带半导体的应用,同步整流IC需进一步提升采样速率与抗干扰能力。例如,下一代芯片可能集成AI算法,实时校正因温度、负载变化导致的精度漂移,实现“智能自适应”控制。

同步整流IC的精度是平衡效率与可靠性的核心要素。从设计、制造到应用的每一个环节,均需兼顾信号完整性与抗干扰能力,方能充分发挥其在电力电子领域的技术优势。