热门关键词:

在智能手机快充、数据中心服务器、新能源逆变器等场景中,**电源转换效率**的微小提升都能带来显著的节能收益。而实现这一目标的核心技术之一,正是**同步整流控制芯片(SR Controller IC)**。这种芯片通过取代传统二极管整流方案,将电源损耗降低30%-50%,成为现代高效电源设计中不可或缺的元件。本文将深入解析其工作原理、关键技术及实际应用,揭开这一“电能搬运工”的神秘面纱。

---

### **一、同步整流的革命性意义**

在传统开关电源中,二次侧的整流环节通常采用肖特基二极管或快恢复二极管。然而,二极管的正向压降(0.3-1V)会导致显著的导通损耗,尤其在低压大电流场景(如5V/20A快充)中,损耗甚至占系统总损耗的40%。**同步整流技术**通过用低导通电阻(RDS(on))的MOSFET替代二极管,将整流损耗降低至传统方案的1/5以下。

**控制芯片的核心任务**在于精准控制MOSFET的开关时序:在变压器次级绕组电压反向时及时关断,避免电流倒灌;在正向导通时快速响应,最大化能效。这种毫秒级的动态调控,正是同步整流控制芯片的技术壁垒所在。

---

### **二、同步整流控制芯片的工作原理**

#### **1. 电压检测与逻辑控制**

芯片通过**电压采样电路**实时监测变压器次级绕组的电压极性。当检测到正向电压(即原边开关管关断、次级开始放电)时,立即生成驱动信号,开启同步整流MOSFET。这一过程需在数十纳秒内完成,否则会导致电流路径中断或反向导通。

#### **2. 死区时间管理**

为避免原边与副边开关管同时导通造成的“直通短路”,芯片必须精确计算**死区时间(Dead Time)**。先进的芯片采用**自适应算法**,根据负载电流和温度动态调整死区,兼顾安全性与效率。例如,在轻载时延长死区以降低开关损耗,重载时缩短死区以提升导通占比。

#### **3. 驱动电路设计**

同步整流MOSFET的栅极需要足够高的驱动电压(通常10-15V)以确保低RDS(on)。控制芯片内部集成**电荷泵**或**自举电路**,将逻辑电平(3.3V/5V)升压至所需驱动电压。部分高端芯片还支持**负压关断技术**,通过施加负电压加速MOSFET关断,进一步减少关断损耗。

### **三、关键技术突破与应用场景**

#### **1. 自适应多模式控制**

为应对宽电压输入(如USB PD 3.1的5-48V)和动态负载(如CPU的瞬间功耗激增),新一代芯片采用**多模式混合控制**:

- **CCM(连续导通模式)**:适用于满载工况,优化导通时间占比;

- **DCM(断续导通模式)**:在轻载时降低开关频率,减少栅极驱动损耗;

- **突发模式(Burst Mode)**:待机状态下进入间歇工作,将待机功耗降至毫瓦级。

#### **2. 集成化与智能化趋势**

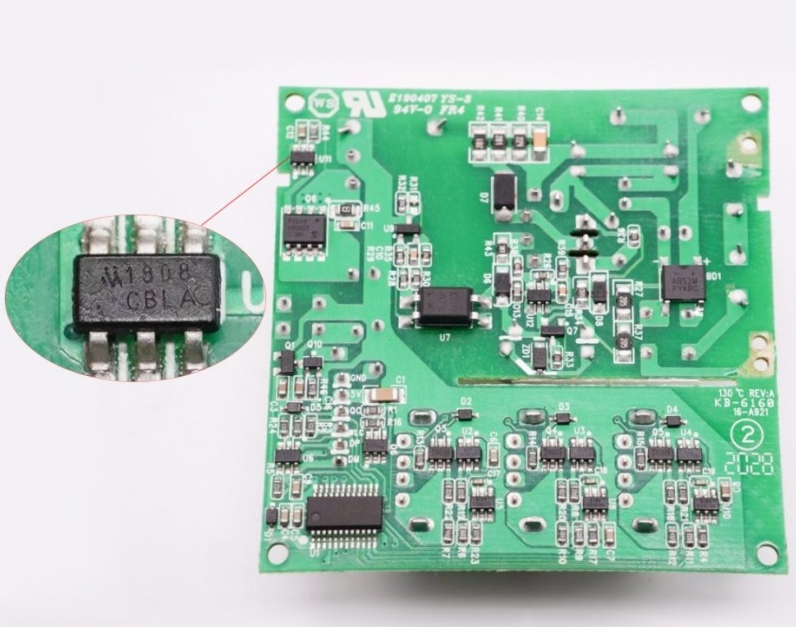

为简化设计,主流芯片(如TI的UCC24630、Infineon的IR11682)已将**高压检测、驱动、保护电路**集成于单一封装。此外,部分产品支持数字接口(I²C/PMBus),允许用户实时调整参数,实现**故障自诊断**与**能效优化**。

#### **3. 典型应用案例**

- **快充适配器**:在GaN+同步整流方案中,效率可达95%以上,支持100W输出而无需散热片;

- **服务器电源**:48V转12V的DC/DC模块中,同步整流可将效率提升至98%,显著降低数据中心PUE值;

- **新能源汽车**:车载OBC(充电机)通过同步整流减少热损耗,提升充电速度与系统可靠性。

---

### **四、设计挑战与解决方案**

#### **1. 时序精度与噪声干扰**

次级绕组的电压振铃(Voltage Ringing)可能导致误触发。为此,芯片需内置**噪声抑制电路**,如施密特触发器或数字滤波算法,确保信号检测的准确性。

#### **2. 热管理与可靠性**

高密度封装下,芯片的功耗与散热成为瓶颈。通过**封装优化**(如QFN、Flip-Chip)和**动态热调节**(根据结温调整驱动强度),可有效延长器件寿命。

#### **3. EMI兼容性**

快速开关带来的电磁干扰(EMI)可能影响系统认证。采用**软开关技术**(如ZVS同步整流)或**频率抖动功能**,可分散谐波能量,轻松通过CISPR 32等标准测试。

---

从上述分析可见,**同步整流控制芯片**不仅是电源效率跃升的“幕后功臣”,更推动了整个电子行业向高效化、小型化迈进。随着5G、AI算力与碳中和需求的爆发,这一领域的技术创新将持续加速,为绿色能源未来提供底层支撑。