### 2.8A,34V High Efficiency Synchronous Step-Down DC/DC Converter

### **Description**

NDP1331KC is a high efficiency, monolithic synchronous step-down DC/DC converter utilizing a constant frequency, average current mode control architecture. Capable of delivering up to 2.8A continuous load with excellent line and load regulation. The device operates from an input voltage range of 7V to 32V and provides an adjustable output voltage from 3.6V to 25V.

The NDP1331KC features short circuit and thermal protection circuits to increase system reliability. The internal soft-start avoids input inrush current during startup.

The NDP1331KC require a minimum number of external components. and a wide array of protection features to enhance reliability

### **Features**

- Wide VIN Range : 7V to 32V

- 2.8A Continuous Output Current

- Up to 93% Efficiency

- CC/CV Mode Control

- 100% Max Duty Cycle

- Built in Adjustable Line-Compensation

- Adjustable Output Voltages

- +/-1.5% Output Voltage Accuracy

- +/- 5% Current Limit Accuracy.

- Integrated 75mΩ High Side Switch

- Integrated 35mΩ Low Side Switch

- Programable Frequency(130KHz~300KHz)

- Burst Mode Operation at Light Load

- Internal loop Compensation

- Internal Soft Start

- Available in SOP8 Package

## **Applications**

- Car Charger

- Rechargeable Portable Devices

- Networking Systems

- Distributed Power Systems

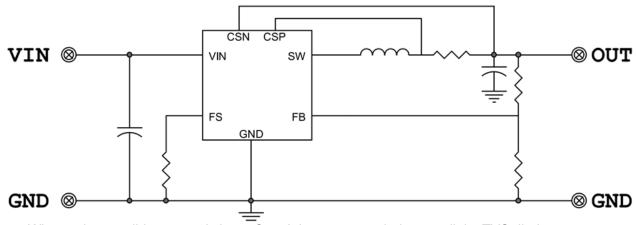

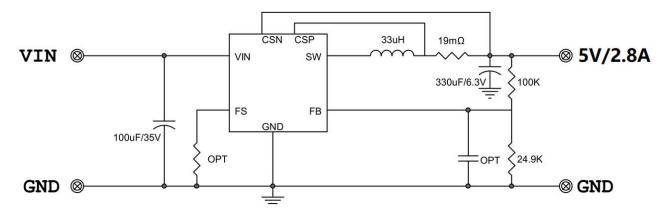

# **Typical Application**

Note: When using a solid or ceramic input Cap, It is recommended to parallel a TVS diode.

www.dcdcic.com May-2020 Rev1.4 Page1-9

# **Absolute Maximum Ratings** (at TA = 25°C)

| Characteristics                             | Symbol        | Rating          | Unit |

|---------------------------------------------|---------------|-----------------|------|

| VIN to GND                                  |               | -0.3 to 34      | V    |

| SW to GND                                   |               | -0.3 to VIN+0.3 | V    |

| FB, FS to GND                               |               | -0.3 to +6      | V    |

| CSP, CSN to GND                             |               | -0.3 to 25      | V    |

| Junction to Ambient Thermal Resistance      |               | 105             | °C/W |

| Operating Junction Temperature              |               | -40 to 150      | °C   |

| Storage Junction Temperature                |               | -55 to 150      | °C   |

| Thermal Resistance from Junction to case    | $\theta_{JC}$ | 45              | °C/W |

| Thermal Resistance from Junction to ambient | $\theta_{JA}$ | 90              | °C/W |

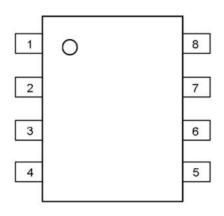

# **Pin Function And Descriptions**

| PIN    | NAME                      | Description               |  |  |

|--------|---------------------------|---------------------------|--|--|

| 1 VFB  |                           | Feedback Of Output        |  |  |

| 1      | VID                       | Voltage                   |  |  |

| 2      | CSP                       | Positive Pole of Current  |  |  |

| Z CSF  |                           | Sense                     |  |  |

| 3      | CSN                       | Negative Pole1 of Current |  |  |

| 3 CSN  | CSN                       | Sense                     |  |  |

| 4      | VIN                       | Power Input Positive Pole |  |  |

| 5.6 CW |                           | Switching,                |  |  |

| 5,6 SW | Connected With a Inductor |                           |  |  |

| 7 FS   |                           | Connect a Resistor to GND |  |  |

| /      | г3                        | for Frequency Config      |  |  |

| 8      | GND                       | Ground                    |  |  |

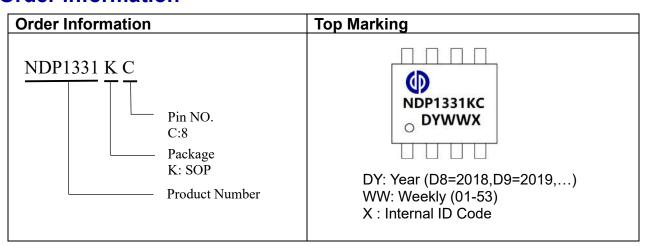

# **Order information**

www.dcdcic.com May-2020 Rev1.4 Page2-9

# **Electrical Characteristics**

TJ = 25°C. VIN = 12V, unless otherwise noted

| Characteristics              | Symbol            | Conditions                        | Min   | Тур  | Max   | Units |

|------------------------------|-------------------|-----------------------------------|-------|------|-------|-------|

| Input Voltage                | VIN               |                                   | 7     | -    | 32    | V     |

| UVLO Voltage                 | V <sub>UVLO</sub> |                                   |       | 5.8  |       | V     |

| UVLO Hysteresis              |                   |                                   |       | 1.4  |       | V     |

| Input over voltage protect   | Vovp              |                                   | 32    |      |       | V     |

| Quiescent Current            | I <sub>CCQ</sub>  | V <sub>FB</sub> = 1.2V, no switch | -     | 1300 | -     | uA    |

| Standby Current              | I <sub>SB</sub>   | No Load                           | -     | 1.7  | 2.2   | mA    |

| FB Reference Voltage         | VFB               |                                   | 0.985 | 1    | 1.015 | V     |

| V <sub>FB</sub> bias Current | lfв               |                                   |       |      | 0.2   | uА    |

| Current Sense AMP            | Vcs               | CSP-CSN                           | 57    | 60   | 63    | mV    |

| 0 "1" =                      | Fsw               | FS Floating                       |       | 130  |       | KHz   |

| Switching Frequency          |                   | connect 470K resister             |       | 300  |       | KHz   |

| FS Shut down                 | VFSEN             |                                   |       | 0.3  | 0.4   | V     |

| Maximum Duty Cycle           |                   |                                   |       | 100  | -     | %     |

| Minimum On-Time              |                   |                                   | -     | 250  | -     | ns    |

| Current Limit                | Ішм               |                                   | 3.5   |      |       | Α     |

| VFB short protect            | VFBscp            |                                   |       | 0.6  |       | V     |

| Hicup Interval               | Thiccup           |                                   |       | 500  |       | mS    |

| Soft start Time              | Tss               |                                   |       | 2    |       | mS    |

| RDS <sub>ON</sub> Of Power   | High side         | Temp=25℃                          |       | 75   |       | mΩ    |

| MOS                          | Low side          | Temp=25℃                          |       | 35   |       | mΩ    |

| Thermal Regulation           | TTR               |                                   |       | 150  |       | °C    |

| Thermal shutdown Temp        | T <sub>SD</sub>   |                                   | -     | 165  | -     | °C    |

| Thermal Shutdown Hysteresis  | T <sub>SH</sub>   |                                   | -     | 30   | -     | °C    |

www.dcdcic.com May-2020 Rev1.4 Page3-9

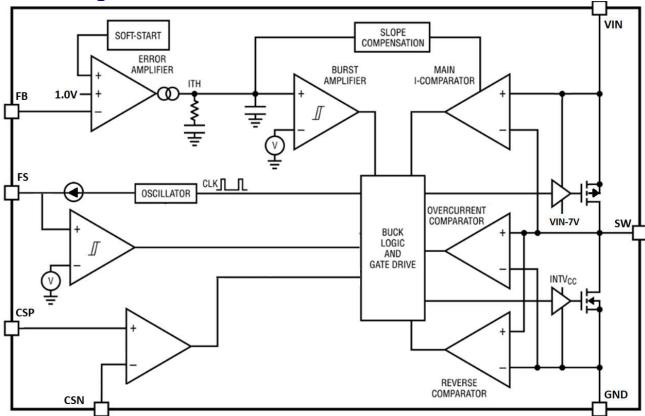

### **Block Diagram**

### **Operation**

The NDP1331KC is a high efficiency, monolithic, synchronous step-down DC/DC converter utilizing а constant frequency, average current mode control architecture. Average current mode control enables fast and precise control of the output current. It operates through a wide VIN range and regulates with low quiescent current. An error amplifier compares the output voltage with a internal reference voltage of 1.0V and adjusts the peak inductor current accordingly, overvoltage and undervoltage comparators will turn off the regulator.

### **Main Control Loop**

During normal operation, the internal top power switch (P-channel MOSFET) is turned on at the beginning of each clock cycle, causing the inductor current to increase. The sensed inductor current is then delivered to the average current amplifier, whose output is compared with a saw-tooth ramp. When the voltage exceeds the vduty voltage, the **PWM** comparator trips and turns off the top power MOSFET. After the top power MOSFET turns off, the synchronous power switch (N-channel MOSFET) turns on, causing the inductor current to decrease. The bottom switch stays on until the beginning of the next clock cycle, unless the reverse current limit is reached and the reverse current comparator trips. In closed-loop operation, the average current amplifier creates an average current loop that forces the average sensed current signal to be equal to the internal ITH voltage. Note that the DC gain and compensation of this average current loop is automatically adjusted to maintain an optimum

www.dcdcic.com May-2020 Rev1.4 Page4-9

current-loop response. The error amplifier adjusts the ITH voltage by comparing the divided-down output voltage (VFB) with a 1.0V reference voltage. If the load current changes, the error amplifier adjusts the average inductor current as needed to keep the output voltage in regulation.

### Low Current operation

The discontinuous-conduction modes (DCMs) are available to control the operation of the NDP1331KC at low currents. Burst Mode operation automatically switch from continuous operation to the Burst Mode operation when the load current is low

### **VIN Overvoltage Protections**

In order to protect the internal power MOSFET devices against transient voltage spikes, the NDP1331KC constantly monitors the VIN pin for an overvoltage condition. When VIN rises above 32V, the regulator suspends operation by shutting off both power MOSFETs. Once VIN drops below 31V, the regulator immediately resumes normal operation. The regulator executes its soft-start function when exiting an overvoltage condition.

#### **Cable Drop Compensation**

Due to the resistive of charger's output Cable, The NDP1331KC built in a simple user programmable cable voltage drop compensation using the impedance at the FB pin. Choose the proper resistance values for charger's output cable as show in table 1:

$R_{\text{up}}$  is the upper resistor the resistors divider net  $R_{\text{low}}$  is the lower resistor the resistors divider net

| Rfb(UPER) (K) | Rlow (K) | Cable Drop<br>compensation<br>(mV) |

|---------------|----------|------------------------------------|

| 100           | 25       | 130                                |

| 160           | 39       | 200                                |

| 360           | 91       | 500                                |

| 470           | 120      | 680                                |

| 820           | 200      | 1200                               |

| 1200          | 300      | 1800                               |

table 1

### **Frequency Selection and Shutdown**

The switching frequency of the NDP1331KC can be programmed through an external resistor between 130kHz and 300 kHz. Floating this pin set the switching frequency to 130K, an external resistor can set the frequency up to 300KHz. the switching frequency is set using the FS pins as shown in Table 1:

| FS Resistor(KΩ) | Frequency(KHz) |

|-----------------|----------------|

| Floating        | 130K           |

| 2000            | 180K           |

| 1000            | 220K           |

| 470             | 300K           |

When the FS pin is below 0.3V, the NDP1331KC enters a low current shutdown state, reducing the DC supply current to 1.3mA.

## **Applications Information**

#### Input Capacitor (CIN) Selection

The input capacitance CIN is needed to filter the square wave current at the drain of the top power MOSFET. To prevent large voltage transients from occurring, a low ESR input capacitor sized for the maximum RMS current should be used. The maximum RMS current is given by:

$$I_{RMS} \cong I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

This formula has a maximum at VIN = 2VOUT, where: IRMS  $\cong$  IOUT/2

www.dcdcic.com May-2020 Rev1.4 Page5-9

This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that current ripple ratings capacitor from manufacturers are often based on only 2000 hours of life which makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet size or height requirements in the design. For low input voltage applications, sufficient bulk input capacitance is needed to minimize transient effects during output load changes.

### **Output Capacitor (COUT) Selection**

The selection of COUT is determined by the effective series resistance (ESR) that is required to minimize voltage ripple and load step transients as well as the amount of bulk capacitance that is necessary to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response. The output ripple,  $\triangle$ VOUT, is determined by:

$$\Delta V_{OUT} < \Delta I_{L} \left( \frac{1}{8 \bullet f \bullet C_{OUT}} + ESR \right)$$

The output ripple is highest at maximum input voltage since  $\triangle$ IL increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, aluminum electrolytic, and ceramic capacitors are all available in surface mount packages. Special polymer capacitors are very low ESR but have lower capacitance Once the value for L is known, the type of inductor must be selected. Actual core loss is independent of core size for a fixed inductor value, but is very dependent on the inductance

density than other types. Tantalum capacitors have the highest capacitance density but it is important to only use types that have been surge tested for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR, but can be used in cost-sensitive applications provided that consideration is given to ripple current ratings and long-term reliability. Ceramic capacitors have excellent low ESR characteristics and small footprints.

#### **Inductor Selection**

Given the desired input and output voltages, the inductor value and operating frequency determine the ripple current:

$$\Delta I_{L} = \frac{V_{OUT}}{f \cdot L} \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

Lower ripple current reduces power losses in the inductor, ESR losses in the output capacitors and output voltage ripple. Highest efficiency operation is obtained at low frequency with small ripple current. However, achieving this requires a large inductor. There is a trade-off between component size, efficiency and operating frequency. A reasonable starting point is to choose a ripple current that is about 40% of IOUT(MAX). To guarantee that ripple current does not exceed a specified maximum, the inductance should be chosen according to:

$$L = \frac{V_{OUT}}{f \cdot \Delta I_{L(MAX)}} \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

selected. As the inductance or frequency increases, core losses decrease. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase.

Copper losses also increase as frequency increases Ferrite designs have very low core losses and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates "hard", which means that inductance collapses abruptly when the peak design current is exceeded. This results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate!

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar characteristics. The choice of which style inductor to use mainly depends on the price versus size requirements and any radiated field/EMI requirements. New designs for surface mount inductors are available from Coilcraft, Toko, Vishay, NEC/Tokin, TDK and Würth Electronik.

temperature of the part. If the junction temperature reaches approximately 165°C, both power switches will be turned off until the temperature drops about 30°C cooler To avoid the NDP1331KC from exceeding the maximum junction temperature, the user will need to do some thermal analysis. The goal of the thermal

#### **Efficiency Considerations**

The percent efficiency of a switching regulator is equal to the output power divided by the input power times 100%. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Percent efficiency can be expressed as: % Efficiency = 100% – (Loss1 + Loss2 + ...) where Loss1, Loss2, etc. are the individual losses as a percentage of input power. Although all dissipative elements in the circuit produce losses, three main sources usually account for most of the losses in NDP1331KC circuits: 1) I2R losses, 2) switching and biasing losses, 3) other losses.

#### **Thermal Conditions**

In a majority of applications, the NDP1331KC does not dissipate much heat due to its high efficiency and low thermal resistance. However, in applications where the NDP1331KC is running at high ambient temperature, high VIN, and maximum output current load, the heat dissipated may exceed the maximum junction

analysis is to determine whether the power dissipated exceeds the maximum junction temperature of the part. If the application calls for a higher ambient temperature and/or higher switching frequency, care should be taken to reduce the temperature rise of the part by using a heat sink or forced air flow.

www.dcdcic.com May-2020 Rev1.4 Page7-9

# **Typical Applications**

www.dcdcic.com May-2020 Rev1.4 Page8-9

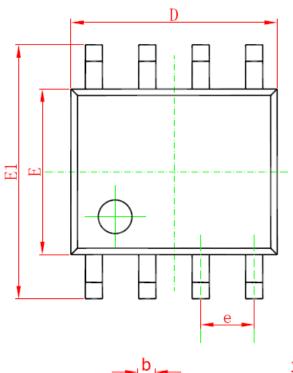

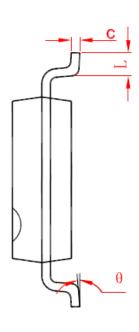

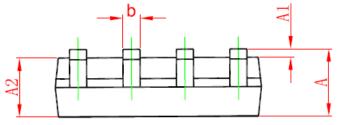

# **Package Description**

8-Lead Standard Small Outline Package [SOP-8]

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |

|--------|---------------------------|-------|----------------------|-------|

| Symbol | Min                       | Max   | Min                  | Max   |

| A      | 1.350                     | 1.750 | 0.053                | 0.069 |

| A1     | 0.050                     | 0.250 | 0.002                | 0.010 |

| A2     | 1.250                     | 1.650 | 0.049                | 0.065 |

| b      | 0.310                     | 0.510 | 0.012                | 0.020 |

| c      | 0.170                     | 0.250 | 0.006                | 0.010 |

| D      | 4.700                     | 5.150 | 0.185                | 0.203 |

| E      | 3.800                     | 4.000 | 0.15                 | 0.157 |

| E1     | 5.800                     | 6.200 | 0.228                | 0.244 |

| e      | 1.270 (BSC)               |       | 0.05 (BSC)           |       |

| L      | 0.400                     | 1.270 | 0.016                | 0.050 |

| θ      | 0°                        | 8°    | 0°                   | 8°    |

www.dcdcic.com May-2020 Rev1.4 Page9-9